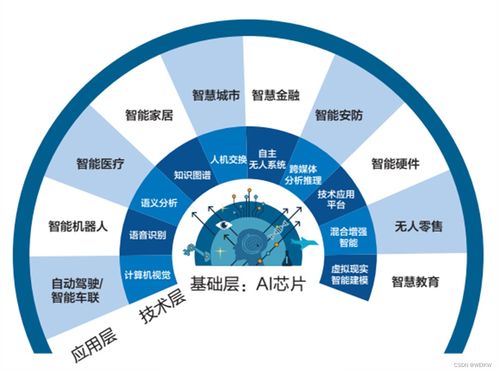

隨著人工智能技術(shù)的快速發(fā)展,神經(jīng)網(wǎng)絡(luò)模型變得越來越復(fù)雜,對(duì)計(jì)算能力的需求呈指數(shù)級(jí)增長。傳統(tǒng)CPU架構(gòu)在處理神經(jīng)網(wǎng)絡(luò)計(jì)算時(shí)效率有限,神經(jīng)網(wǎng)絡(luò)硬件加速器應(yīng)運(yùn)而生,成為推動(dòng)AI應(yīng)用落地的關(guān)鍵技術(shù)。本文將從架構(gòu)設(shè)計(jì)和技術(shù)開發(fā)兩個(gè)維度深入探討神經(jīng)網(wǎng)絡(luò)硬件加速器。

一、神經(jīng)網(wǎng)絡(luò)硬件加速器架構(gòu)設(shè)計(jì)

1. 主流架構(gòu)類型

- 專用集成電路(ASIC)架構(gòu):如Google的TPU、華為的昇騰系列,專門為神經(jīng)網(wǎng)絡(luò)計(jì)算優(yōu)化,具有最高的能效比

- 現(xiàn)場(chǎng)可編程門陣列(FPGA)架構(gòu):如Xilinx的Versal系列,提供靈活性,支持算法迭代更新

- 圖形處理器(GPU)架構(gòu):如NVIDIA的Tensor Core GPU,兼具通用性和高性能

- 神經(jīng)形態(tài)計(jì)算架構(gòu):模擬生物神經(jīng)網(wǎng)絡(luò),具有極低功耗特性

2. 核心架構(gòu)組件

- 張量處理單元(TPU):專門針對(duì)矩陣乘法和卷積運(yùn)算優(yōu)化

- 內(nèi)存層次結(jié)構(gòu):多級(jí)緩存設(shè)計(jì),減少數(shù)據(jù)搬運(yùn)開銷

- 數(shù)據(jù)流控制器:實(shí)現(xiàn)計(jì)算與數(shù)據(jù)搬運(yùn)的并行化

- 互聯(lián)架構(gòu):支持多核協(xié)同計(jì)算的高速互聯(lián)網(wǎng)絡(luò)

3. 架構(gòu)優(yōu)化策略

- 數(shù)據(jù)復(fù)用優(yōu)化:通過數(shù)據(jù)局部性原理減少內(nèi)存訪問

- 計(jì)算并行化:充分利用空間和時(shí)間并行性

- 精度可配置:支持混合精度計(jì)算,平衡精度與性能

- 功耗管理:動(dòng)態(tài)電壓頻率調(diào)節(jié)等低功耗技術(shù)

二、神經(jīng)網(wǎng)絡(luò)硬件加速器技術(shù)開發(fā)

1. 開發(fā)流程與方法論

- 需求分析階段:明確目標(biāo)工作負(fù)載和性能指標(biāo)

- 架構(gòu)探索階段:通過建模和仿真確定最優(yōu)架構(gòu)

- RTL設(shè)計(jì)與驗(yàn)證:使用硬件描述語言實(shí)現(xiàn)設(shè)計(jì)

- 物理設(shè)計(jì)與流片:完成布局布線和芯片制造

- 系統(tǒng)集成與測(cè)試:軟硬件協(xié)同驗(yàn)證和性能調(diào)優(yōu)

2. 關(guān)鍵技術(shù)挑戰(zhàn)

- 內(nèi)存墻問題:計(jì)算單元與內(nèi)存帶寬不匹配

- 功耗約束:在有限功耗預(yù)算內(nèi)實(shí)現(xiàn)高性能

- 編程模型:降低開發(fā)難度,提高易用性

- 可擴(kuò)展性:支持不同規(guī)模的計(jì)算需求

3. 開發(fā)工具鏈

- 高級(jí)綜合工具:如Xilinx Vitis HLS、Intel HLS

- 神經(jīng)網(wǎng)絡(luò)編譯器:如TVM、MLIR

- 性能分析工具:提供詳細(xì)的性能剖析和瓶頸分析

- 驗(yàn)證平臺(tái):確保功能正確性和性能達(dá)標(biāo)

三、發(fā)展趨勢(shì)與未來展望

神經(jīng)網(wǎng)絡(luò)硬件加速器正朝著更高效、更靈活、更智能的方向發(fā)展:

- 異構(gòu)計(jì)算融合:CPU、GPU、專用加速器協(xié)同工作

- 存算一體架構(gòu):突破內(nèi)存瓶頸的新型計(jì)算范式

- 可重構(gòu)計(jì)算:根據(jù)工作負(fù)載動(dòng)態(tài)調(diào)整硬件結(jié)構(gòu)

- 算法-硬件協(xié)同設(shè)計(jì):軟硬件深度優(yōu)化提升整體效率

四、開發(fā)實(shí)踐建議

對(duì)于開發(fā)者而言,成功開發(fā)神經(jīng)網(wǎng)絡(luò)硬件加速器需要:

- 深入理解神經(jīng)網(wǎng)絡(luò)計(jì)算特征和數(shù)據(jù)流模式

- 掌握現(xiàn)代數(shù)字電路設(shè)計(jì)和驗(yàn)證方法

- 熟悉EDA工具鏈和開發(fā)流程

- 關(guān)注行業(yè)最新技術(shù)動(dòng)態(tài)和標(biāo)準(zhǔn)演進(jìn)

- 建立跨學(xué)科團(tuán)隊(duì),融合算法、硬件、軟件專業(yè)知識(shí)

神經(jīng)網(wǎng)絡(luò)硬件加速器的架構(gòu)創(chuàng)新和技術(shù)突破將持續(xù)推動(dòng)人工智能技術(shù)的發(fā)展,為各行各業(yè)帶來革命性的變革。隨著技術(shù)的成熟和成本的降低,專用AI加速器將在邊緣計(jì)算、自動(dòng)駕駛、智能物聯(lián)網(wǎng)等領(lǐng)域發(fā)揮越來越重要的作用。